AMBA AXI Specification Introduction

AMBA AXI介绍

AMBA(Advanced Microcontroller Bus Architecture) AXI(Advanced eXtensible Interface)是ARM公司推出的一种高性能、低延迟、可扩展的系统级总线标准,是AMBA总线协议中最新的一代,AMBA AXI的Specitication可以在官网下载。

AMBA AXI协议支持高性能高频的系统设计,该协议拥有以下优点:

适合高带宽和低延迟的设计

不需要复杂的桥即可提供高频操作

可以满足多种组件的接口需求

适合高初始访问延迟的存储器控制器

提供互联架构实现的灵活性

向后兼容AHB与APB接口

同时,该协议还拥有以下特点:

分离的地址/控制和数据阶段

通过使用字节选通信号的方式支持非对齐数据传输

使用突发传输时只需要传输起始地址

允许地址信息提前于实际数据传输发送

分离的读写数据通道,这可以提供低损耗的DMA

支持发出多个未完成的地址

支持乱序传输完成

允许简单添加寄存器阶段以提供时序收敛

AXI协议同时包含了低功耗操作所需的信号扩展,也包含了AXI4-Lite协议,该协议是AXI4的子集,有着更简单的控制寄存器接口和组件。

AXI结构

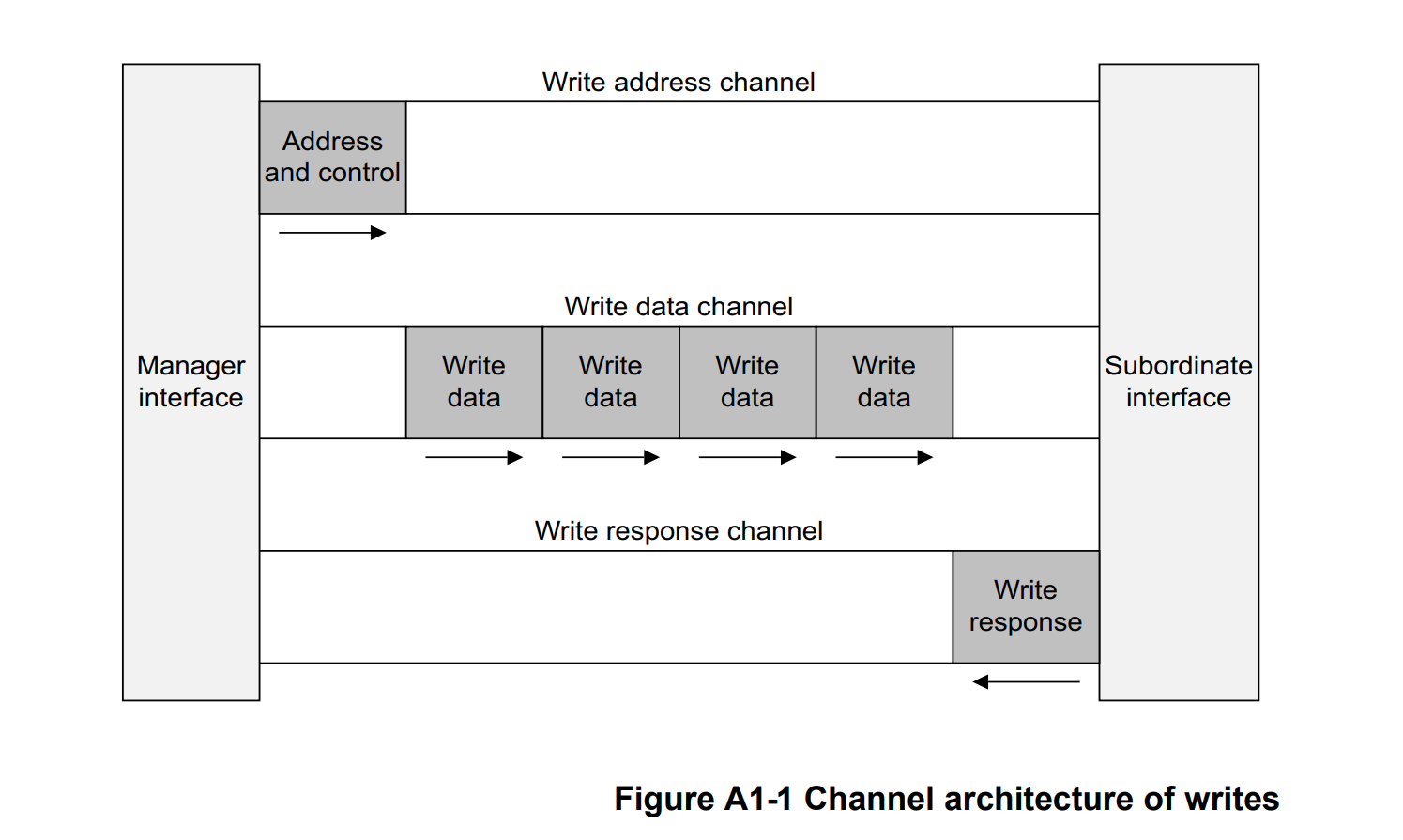

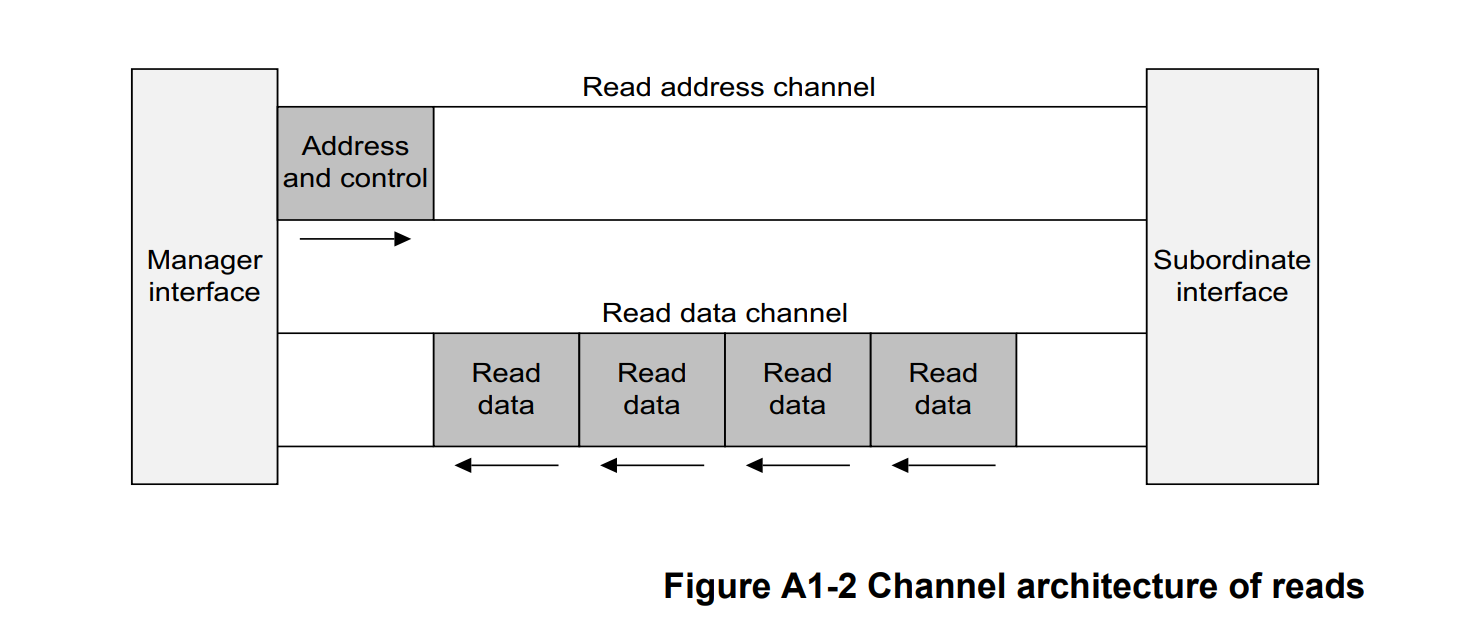

AXI是一种基于突发事务的总线协议,AXI一共有五个通道分别为:

- Read Address : 读地址通道,简称AR

- Read Data : 读数据通道,简称R

- Write Address : 写地址通道,简称AW

- Write Data : 写数据通道,简称W

- Write Response : 读响应通道,简称B

其中可以分为两大类,地址通道和数据通道,地址通道携带需要传输数据的控制信息,数据通道进行数据的交互。AXI总线的两端分别为Master和Slave,可以根据地址通道或数据通道的方向来判断总线方向。

下图分别展示在读事务和写事务下,AXI各个通道的方向。

在官方的文档中,ARM喜欢把AXI的两端命名成Manager和Subordinate,但是一般大家都叫Master和Slave。

寄存器切片

第一次看文档并没有注意到Introduction章节有一小部分讲的是寄存器切片(Register Slice),之后了解寄存器切片后再看文档中的这段话,有种豁然开朗的感觉,今后我会单独发布一篇关于Register Slice的博客。那么先让我们来看看原文是怎么说的:

Each AXI channel transfers information in only one direction, and the architecture does not require any fixed relationship between the channels. These qualities mean that a register slice can be inserted at almost any point in any channel, at the cost of an additional cycle of latency.

AXI的每个通道都只会往一个方向发送消息,并且这种结构并不要求各个通道间有固定的关系。这些特点意味着Register Slice可以被插入在AXI的任意通道,而代价只有一个周期的延迟。

这段话后面还有一段注释:

These qualities make the following possible:

- Trade-off between cycles of latency and maximum frequency of operation.

- Direct, fast connection between a processor and high-performance memory, but to use simple register slices to isolate a longer path to less performance critical peripherals.

首先我们可以简单定义这种特性:一种通道内数据流确定,且各个通道无固定关系的总线。

思索很久,词穷的我实在没有想到如何命名,那么可以求助强大的GPT。有一说一,感觉说的挺好^ ^。

继续上文翻译,AXI的这种无状态性,可以使得

- AXI可以在latency和操作的最大频率做权衡。

- 对于处理器和高性能内存之间可以进行直接、快速连接,对于性能要求不是很高外设的较长路径,可以通过简单的RegSlice进行隔离。

如何分析以上两句话,首先对于第一句,我感觉Opreation这个词用的不是很对,如果换成implementation可能更好,我们都知道如果你要想综合出更高的频率,可以通过插入Pipe,这里的RegSlice其实和Pipe的功能有些类似,但是插入Pipe会带来Latency的增加,具体案例可以参考DDR4和DDR5,虽然DDR5的频率更高,但是代价就是Latency大。由此可以衍生出第二句话,不同Performance要求IP的权衡,对于高性能的IP例如Cache、内存这种可以让处理器通过AXI直接连接,使得Latency低,但是对于要求不高的IP可以使处理器距离IP远一点,如果综合不了就可以用RegSlice进行Timing的隔断,固然这也会使得Latency增加。

AXI信号描述

AXI的信号描述按照通道进行分组。

Write address channel

| Name | Width | Desprition |

|---|---|---|

| AWADDR | 写地址,突发操作中第一次数据传出的地址 | |

| AWSIZE | [2:0] | 突发大小,突发传输的传输字节大小 |

| AWLEN | [7:0] | 突发长度,突发传输的传输次数 |

| AWBURST | [1:0] | 突发类型,包括FIXED、INCR、WRAP |

| AWID | 写地址ID,标识写事务的名称 | |

| AWLOCK | [0:0] | 锁定类型,原子访问标识信号 |

| AWPROT | [2:0] | 保护类型,写入事务的保护属性 |

| AWQOS | [3:0] | 服务质量,标识写传输的优先级 |

| AWREGION | [3:0] | 区域标识,标识访问Slave的区域 |

| AWUSER | 用户定义信号,挂在AW通道的用户定义信号 | |

| AWVALID | Master标识给Slave的写地址通道数据有效 | |

| AWREADY | Slave标识给Master自身准备好接收写控制信号 |